# RISC-V

RISC-V 是一个新的开源精简指令集体系架构(ISA),诞生于美国加州大学伯克利分校,RISC-V 架构相比主流的指令集架构更加简洁、灵活。自2016年 RISC-V 基金会成立以来,RISC-V 受到了广泛的关注,并被业界高度接纳。国内也产生众多 RISC-V 架构的处理器芯片,例如嘉楠 K210。--摘自《RISC-V架构与嵌入式开发快速入门--胡振波著》

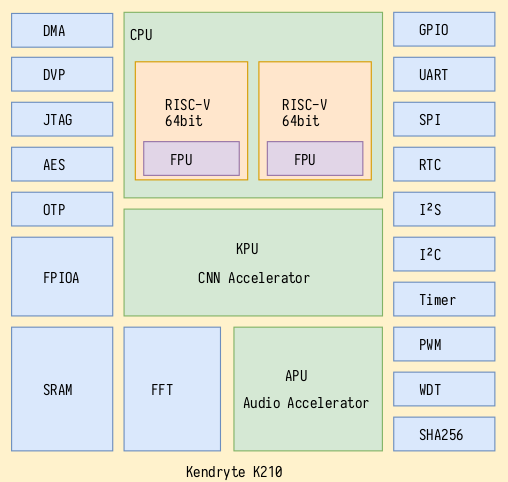

下面以kendryte K210为例介绍RISC-V芯片的特性,以下内容摘自 K210 技术规格书 (opens new window)。

# 概述

Kendryte K210 是一款基于 RISC-V 架构且集成机器视觉与机器听觉能力的系统级芯片(SoC),具有双核64位处理器,拥有较好的功耗性能,稳定性与可靠性,温度范围-40°C 到 125°C。芯片系统架构如下图所示:

K210 包含 RISC-V 64位双核 CPU,每个核心内置独立FPU。 K210 内嵌AES与SHA256算法加速器,提供安全功能。 K210 拥有高性能、低功耗的SRAM,以及功能强大的DMA,在数据吞吐能力方面性能优异。 K210 具备丰富的外设单元,分别是:DVP、JTAG、OTP、FPIOA、GPIO、UART、SPI、RTC、I²S、I²C、 WDT、Timer 与 PWM,可满足海量应用场景。

# 功能描述

# 中央处理器 (CPU)

# 基本特性

| 项目 | 内容 | 描述 |

|---|---|---|

| 核心数量 | 2核心 | 双核对等,各个核心具备独立FPU |

| 处理器位宽 | 64位 | 64位CPU位宽,为高性能算法计算提供位宽基础,计算带宽充足 |

| 标称频率 | 400MHz | 频率可调,可通过调整PLL VCO与分频进行变频 |

| 指令集扩展 | IMAFDC | 基于 RISC-V 64位IMAFDC (RV64GC),胜任通用任务 |

| 浮点处理单元 | 双精度 | 具备乘法器、除法器与平方根运算器,支持单精度、双精度的浮点计算 |

| 平台中断管理 | PLIC | 支持高级中断管理,支持64个外部中断源路由到2个核心 |

| 本地中断管理 | CLINT | 支持CPU内置定时器中断与跨核心中断 |

| 指令缓存 | 32KiB×2 | 核心0与核心1各具有32千字节的指令缓存,提升双核指令读取效能 |

| 数据缓存 | 32KiB×2 | 核心0与核心1各具有32千字节的数据缓存,提升双核数据读取效能 |

| 片上 SRAM | 8MiB | 共计8兆字节的片上 SRAM |

# FPU 与浮点计算能力

- FPU 满足 IEEE754-2008 标准,计算流程按照流水线方式进行,具备很强的运算能力

- 核心 0 与核心 1 各具备独立 FPU,两个核心皆可胜任高性能硬件浮点计算

- 支持 F 扩展,即单精度浮点扩展,CPU 内嵌的 FPU 支持单精度浮点硬件加速

- 支持 D 扩展,即双精度浮点扩展,CPU 内嵌的 FPU 支持双精度浮点硬件加速

- FPU 具备除法器,支持单精度、双精度浮点的硬件除法运算

- FPU 具备平方根运算器,支持单精度、双精度的浮点的硬件平方根运算

# 高级中断管理能力

RISC-V CPU 的 PLIC 控制器支持灵活的高级中断管理,可分7个优先级配置64个外部中断源,两个核心都可独立进行配置:

- 可对两个核心独立进行中断管理与中断路由控制

- 支持软件中断,并且双核心可以相互触发跨核心中断

- 支持 CPU 内置定时器中断,两个核心都可自由配置

- 高级外部中断管理,支持64个外部中断源,每个中断源可配置7个优先级

# 调试能力

- 支持性能监控指令,可统计指令执行周期

- 具备用于调试的高速 UART 与 JTAG 接口

- 支持 DEBUG 模式以及硬件断点

# 神经网络处理器 (KPU)

KPU 是通用神经网络处理器,内置卷积、批归一化、激活、池化运算单元,可以对人脸或物体进行实时检测,具体特性如下:

- 支持主流训练框架按照特定限制规则训练出来的定点化模型

- 对网络层数无直接限制,支持每层卷积神经网络参数单独配置,包括输入输出通道数目、输入输出行宽列高

- 支持两种卷积内核 1x1 和 3x3

- 支持任意形式的激活函数

- 实时工作时最大支持神经网络参数大小为 5.5MiB 到 5.9MiB

- 非实时工作时最大支持网络参数大小为(Flash 容量-软件体积)

| 工况 | 最大定点模型大小(MiB) | 量化前浮点模型大小(MiB) |

|---|---|---|

| 实时(≥ 30fps) | 5.9 | 11.8 |

| 非实时(< 10fps)* 1 | 与Flash容量相关 * 2 | 与Flash容量相关 |

# 音频处理器 (APU)

APU 前处理模块负责语音方向扫描和语音数据输出的前置处理工作。APU前处理模块的功能特性有:

- 可以支持最多8路音频输入数据流,即4路双声道

- 可以支持多达16个方向的声源同时扫描预处理与波束形成

- 可以支持一路有效的语音数据流输出

- 内部音频信号处理精度达到16位

- 输入音频信号支持12位,16位,24位,32位精度

- 支持多路原始信号直接输出

- 可以支持高达192K采样率的音频输入

- 内置FFT变换单元,可对音频数据提供512点快速傅里叶变换

- 利用系统 DMAC 将输出数据存储到 SoC 的系统内存中

# 静态随机存取存储器 (SRAM)

SRAM 包含两个部分,分别是 6MiB 的片上通用 SRAM 存储器与 2MiB 的片上 AI SRAM 存储器,共计 8MiB(1MiB 为 1 兆字节)。其中,AI SRAM 存储器是专为 KPU 分配的存储器。它们分布在连续的地址空 间中,不仅可以通过经由 CPU 的缓存接口访问,而且可以通过非缓存接口直接访问。 SRAM 映射分布:

| 模块名称 | 映射类型 | 开始地址 | 结束地址 | 空间大小 |

|---|---|---|---|---|

| 通用SRAM存储器 | 经CPU缓存 | 0x80000000 | 0x805FFFFF | 0x600000 |

| AI SRAM存储器 | 经CPU缓存 | 0x80600000 | 0x807FFFFF | 0x200000 |

| 通用SRAM存储器 | 非CPU缓存 | 0x40000000 | 0x405FFFFF | 0x600000 |

| AI SRAM存储器 | 非CPU缓存 | 0x40600000 | 0x407FFFFF | 0x200000 |

# 通用 SRAM 存储器

通用SRAM存储器在芯片正常工作的任意时刻都可以访问。该存储器分为两个 Bank,分别为 MEM0 与 MEM1 ,并且 DMA 控制器可同时操作不同 Bank。 通用 SRAM 存储器地址空间:

| 模块名称 | 映射类型 | 开始地址 | 结束地址 | 空间大小 |

|---|---|---|---|---|

| MEM0 | 经CPU缓存 | 0x80000000 | 0x803FFFFF | 0x400000 |

| MEM1 | 经CPU缓存 | 0x80400000 | 0x805FFFFF | 0x200000 |

| MEM0 | 非CPU缓存 | 0x40000000 | 0x403FFFFF | 0x400000 |

| MEM1 | 非CPU缓存 | 0x40400000 | 0x405FFFFF | 0x200000 |

# AI SRAM 存储器

AI SRAM存储器仅在以下条件都满足时才可访问:

- PLL1已使能,时钟系统配置正确

- KPU没有在进行神经网络计算

AI SRAM存储器地址空间:

| 模块名称 | 映射类型 | 开始地址 | 结束地址 | 空间大小 |

|---|---|---|---|---|

| AI SRAM存储器 | 经CPU缓存 | 0x80600000 | 0x807FFFFF | 0x200000 |

| AI SRAM存储器 | 非CPU缓存 | 0x40600000 | 0x407FFFFF | 0x200000 |

# 系统控制器 (SYSCTL)

控制芯片的时钟,复位和系统控制寄存器。

- 配置 PLL 的频率

- 配置时钟选择

- 配置外设时钟的分频比

- 控制时钟使能

- 控制模块复位

- 选择 DMA 握手信号

# 现场可编程 IO 阵列 (FPIOA/IOMUX)

FPIOA 允许用户将 255 个内部功能映射到芯片外围的 48 个自由 IO 上。

- 支持 IO 的可编程功能选择

- 支持 IO 输出的 8 种驱动能力选择

- 支持 IO 的内部上拉电阻选择

- 支持 IO 的内部下拉电阻选择

- 支持 IO 输入的内部施密特触发器设置

- 支持 IO 输出的斜率控制

- 支持内部输入逻辑的电平设置

# 一次性可编程存储器 (OTP)

OTP 是一次性可编程存储器单元,具体应用特性如下:

- 具有 128 Kbit 的大容量存储空间

- 内部划分多个容量不同的 BLOCK,每个 BLOCK 对应一个写保护位,可以单独进行写保护操作

- 具有坏点修复功能

- 内部存储了 64 个 REGISTER_ENABLE 标志位,可以作为控制某些 SoC 的硬件电路行为的开关

- 可以存储 128 位的 AES 加密和解密需要的 KEY,由硬件实现只写可信存储区

# 高级加密加速器 (AES Accelerater)

AES 加速器是用来加密和解密的模块,具体性能如下:

- 支持 ECB,CBC,GCM 三种加密方式

- 支持 128 位,192 位,256 位三种长度的 KEY

- KEY 可以通过软件配置,受到硬件电路保护

- 支持 DMA 传输

# 数字视频接口 (DVP)

DVP 是摄像头接口模块,特性如下:

- 支持 DVP 接口的摄像头

- 支持 SCCB 协议配置摄像头寄存器

- 最大支持 640 X 480 及以下分辨率,每帧大小可配置

- 支持 YUV422 和 RGB565 格式的图像输入

- 支持图像同时输出到 KPU 和显示屏

- 输出到 KPU 的格式可选 RGB888,或 YUV422 输入时的 Y 分量

- 输出到显示屏的格式为 RGB565

- 检测到一帧开始或一帧图像传输完成时可向 CPU 发送中断

# 快速傅里叶变换加速器 (FFT Accelerater)

FFT 加速器用硬件的方式来实现 FFT 的基 2 时分运算。

- 支持多种运算长度,即支持 64 点、128 点、256 点以及 512 点运算

- 支持两种运算模式,即 FFT 以及 IFFT 运算

- 支持可配的输入数据位宽,即支持 32 位及 64 位输入

- 支持可配的输入数据排列方式,即支持虚部、实部交替,纯实部以及实部、虚部分离三种数据排列方式

- 支持 DMA 传输

# 安全散列算法加速器 (SHA256 Accelerater)

SHA256 加速器是用来计算 SHA-256 的计算单元。

- 支持 SHA-256 的计算

- 支持输入数据的 DMA 传输

# 外设模块

# 通用异步收发传输器 (UART)

# 高速 UART:

高速 UART 为 UARTHS(UART0)。

- 通信速率可达 5Mbps

- 8 字节发送和接收 FIFO

- 可编程式 THRE 中断

- 不支持硬件流控制或其他调制解调器控制信号,或同步串行数据转换器

# 通用 UART

通用 UART 为 UART1、UART2 和 UART3,支持异步通信(RS232、RS485 和 IRDA),通信速率可达到5Mbps。 UART 支持 CTS 和 RTS 信号的硬件管理以及软件流控 (XON 和 XOFF)。3 个接口均可被 DMA 访问或者 CPU 直接访问。

- 8 字节发送和接收 FIFO

- 异步时钟支持

- 为了应对 CPU 对于数据同步的对波特率的要求, UART 可以单独配置数据时钟。 全双工模式能保证两个时钟域中数据的同步

- RS485 接口支持

- UART 可以配置为软件可编程式 RS485 模式。默认为 RS232 模式

- 可编程式 THRE 中断

- 用 THRE 中断模式来提升串口性能。当 THRE 模式和 FIFO 模式被选择之后,如果 FIFO 中少于阈值便触发 THRE 中断

# 看门狗定时器 (WDT)

WDT 是 APB 的一种从外设,并且也是 “同步化硬件组件设计” 的组成部分。具有两个 WDT, 分别为 WDT0、WDT1。 看门狗定时器主要包含模块有:

- 一个 APB 从接口

- 一个当前计数器同步的寄存器模块

- 一个随着计数器递减的中断/系统重置模块和逻辑控制电路

- 一个同步时钟域来为异步时钟同步做支持

看门狗定时器支持如下设置:

- APB 总线宽度可配置为 8、16 和 32 位

- 时钟计数器从某一个设定的值递减到 0 来指示时间的计时终止

- 可选择的外部时钟使能信号,用于控制计数器的计数速率

- 一个时钟超时 WDT 可以执行以下任务

- 产生一个系统复位信号

- 首先产生一个中断,即使该位是否已经被中断服务清除,其次它会产生一个系统复位信号

- 占空比可编程调节

- 可编程和硬件设定计数器起始值

- 计数器重新计时保护

- 暂停模式,仅当使能外部暂停信号时

- WDT 偶然禁用保护

- 测试模式,用来进行计数器功能测试(递减操作)

- 外部异步时钟支持。当该项功能启用时,将会产生时钟中断和系统重置信号,即使 APB 总线时钟关闭的情况下

# 通用输入/输出接口 (GPIO)

# 高速 GPIO:

高速 GPIO 为 GPIOHS,共 32 个。具有如下特点:

- 可配置输入输出信号

- 每个 IO 具有独立中断源

- 中断支持边沿触发和电平触发

- 每个 IO 可以分配到 FPIOA 上 48 个管脚之一

- 可配置上下拉,或者高阻

# 通用 GPIO:

通用 GPIO 共 8 个,具有如下特点:

- 8 个 IO 使用一个中断源

- 可配置输入输出信号

- 可配置触发 IO 总中断,边沿触发和电平触发

- 每个 IO 可以分配到 FPIOA 上 48 个管脚之一

- 可配置上下拉,或者高阻

# 直接内存存取控制器 (DMAC)

DMAC 具有高度可配置化,高度可编程,在总线模式下传输数据具有高效率,DMAC 控制器具有多主机,多频道等特点。 DMAC 具有如下特点:

- 内存-内存,内存-外设,外设-内存,外设-外设的 DMA 传输

- 具有独立的核心,主接口和从接口独立时钟

- 当所有外设不活动时主接口可以关闭其时钟来省电

- 多达八个通道,每路通道都有源和目的地对

- 每个通道数据传输数据时每个时刻只能有一个方向传输,不同通道则不受影响

- 输入管脚可以动态选择大小端制式

- 通道锁支持,支持内部通道仲裁,根据数据传输的优先级来使用主接口总线的特权

- DMAC 状态输出,空闲/忙指示

- DMA 传输分配成传输中,被中断,传输完成等传输等级

# 集成电路内置总线 (I²C)

集成电路总线有 3 个 I²C 总线接口,根据用户的配置,总线接口可以用作 I²C MASTER 或 SLAVE 模 式。I²C 接口支持:

- 标准模式(0 到 100Kb/s)

- 快速模式(<= 400Kb/s)

- 7-位/10-位 寻址模式

- 批量传输模式

- 中断或轮询模式操作

# 串行外设接口 (SPI)

串行外设接口有 4 组 SPI 接口,其中 SPI0、SPI1、SPI3 只能工作在 MASTER 模式,SPI2 只能工作在SLAVE 模式, 他们有如下特性:

- 支持 1/2/4/8 线全双工模式

- SPI0、SPI1、SPI2 可支持 25MHz 时钟(待测更新)

- SPI3 最高可支持 100MHz 时钟(待测更新)

- 支持 32 位宽、32BYTE 深的 FIFO

- 独立屏蔽中断 - 主机冲突,发送 FIFO 溢出,发送 FIFO 空,接收 FIFO 满,接收 FIFO 下溢,接收 FIFO 溢出中断都可以被屏蔽独立

- 支持 DMA 功能

- 支持双沿的 DDR 传输模式

- SPI3 支持 XIP

# 集成电路内置音频总线 (I²S)

集成电路内置音频总线共有 3 个 (I²S0、I²S1、I²S2),都是 MASTER 模式。其中 I²S0 支持可配置连 接语音处理模块,实现语音增强和声源定向的功能。下面是一些共有的特性:

- 总线宽度可配置为 8,16 和 32 位

- 每个接口最多支持 4 个立体声通道

- 由于发送器和接收器的独立性,所以支持全双工通讯

- APB 总线和 I²S SCLK 的异步时钟

- 音频数据分辨率为 12,16,20,24 和 32 位

- I²S0 发送 FIFO 深度为 64 字节, 接收为 8 字节,I²S1 和 I²S2 的发送和接收 FIFO 深度都为 8字节

- 支持 DMA 传输

- 可编程 FIFO 阈值

# 定时器 (TIMER)

系统有 3 个 TIMER 模块,它们有如下特性:

- 32 位计数器宽度

- 可配置的向上/向下时基计数器:增加或减少

- 时钟独立可配

- 每个中断的可配置极性

- 单个或组合中断输出标志可配置

- 每个定时器有读/写一致性寄存器

- 定时器切换输出,每当定时器计数器重新加载时切换

- 定时器切换输出的脉冲宽度调制 (PWM),0 %到 100% 占空比

# 只读存储器 (ROM)

AXI ROM 负责从 SPI FLASH 中拷贝程序至芯片的 SRAM 中。

- 支持固件 AES-128-CBC 解密

- 支持 UOP 模式烧写 FLASH 的程序

- 支持固件 SHA256 完整性校验防篡改

- 支持 OTP 中禁用掉 UOP 模式,SHA256 校验,AES 解密

- 支持进入 TURBO 模式,可以使得启动时芯片及其外设以较高频率运行

# 实时时钟 (RTC)

RTC 是用来计时的单元,在设置时间后具备计时功能:

- 可使用外部高频晶振进行计时

- 可配置外部晶振频率与分频

- 支持万年历配置,可配置的项目包含世纪、年、月、日、时、分、秒与星期

- 可按秒进行计时,并查询当前时刻

- 支持设置一组闹钟,可配置的项目包含年、月、日、时、分、秒,闹钟到达时触发中断

- 中断可配置,支持每日、每时、每分、每秒触发中断

- 可读出小于 1 秒的计数器计数值,最小刻度单位为外部晶振的单个周期

- 上电/复位后数据清零

# 脉冲宽度调制器 (PWM)

PWM 用于控制脉冲输出的占空比。 用户可配置 PWM 定时器模块的以下功能:

- 通过指定 PWM 定时器频率或周期来控制事件发生的频率

- 配置特定 PWM 定时器与其他 PWM 定时器或模块同步

- 使 PWM 定时器与其他 PWM 定时器或模块同相

- 设置定时器计数模式:递增,递减,或递增递减循环计数模式

- 使用预分频器更改 PWM 定时器时钟(PT_clk)的速率。每个定时器都有自己的预分频器,通过 寄存器 PWM_TIMER0_CFG0_REG 的 PWM_TIMERx_PRESCALE 配置。PWM 定时器根据该寄存器的设置以较慢的速度递增或递减